| Nom   | • |

|-------|---|

| TIOIT |   |

Prénom:

## ECOLE POLYTECHNIQUE UNIVERSITAIRE DE NICE SOPHIA-ANTIPOLIS

Cycle Initial Polytech Première Année Année scolaire 2009/2010

## Epreuve d'électronique analogique N°2

Mardi 17 Mars 2009

Durée: 1h30

- Cours et documents non autorisés.

- □ Calculatrice de l'école autorisée.

- □ Vous répondrez directement sur cette feuille.

- □ Tout échange entre étudiants (gomme, stylo, réponses...) est interdit

- □ Vous êtes prié:

- d'indiquer votre nom et votre prénom.

- d'éteindre votre téléphone portable (- 1 point par sonnerie).

#### **RAPPELS:**

| Impédance               | $\begin{bmatrix} \mathbf{V}_1 \\ \mathbf{V}_2 \end{bmatrix} = \begin{bmatrix} \mathbf{Z}_{11} & \mathbf{Z}_{12} \\ \mathbf{Z}_{21} & \mathbf{Z}_{22} \end{bmatrix} \begin{bmatrix} \mathbf{I}_1 \\ \mathbf{I}_2 \end{bmatrix}$ | $\begin{cases} V_1 = Z_{11}.I_1 + Z_{12}.I_2 \\ V_2 = Z_{21}.I_1 + Z_{22}.I_2 \end{cases}$ |

|-------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------|

| Quadripôles en<br>série | $V_1$ $Z$ $V_2$                                                                                                                                                                                                                | [Z] = [Z'] + [Z'']                                                                         |

| Impédance d'une capacité C | 1/(jCω) [Ω] |

|----------------------------|-------------|

| Impédance d'une self L     | jLω [Ω]     |

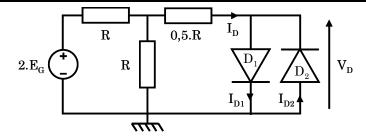

On considère le circuit électrique de la figure (I.1) où les diodes  $D_1$  et  $D_2$  ne forment qu'un seul composant dont la caractéristique  $I_D(V_D)$  est donnée à la figure (I.2). La résistance R a pour valeur  $50~\Omega$ .

Figure I.1.

I.1. Donner l'expression de la droite de charge I<sub>D</sub>(V<sub>D</sub>) du circuit de la figure (I.1) (0.5 pt)

$$\mathbf{E}_G = \mathbf{R}.\mathbf{I}_D + \mathbf{V}_D \quad \text{d'où} \quad \mathbf{I}_D = \frac{\mathbf{E}_G - \mathbf{V}_D}{R}$$

I.2. A partir de la figure (I.2) qui met en évidence les courants respectifs des deux diodes, donner la valeur des tensions de seuil et des résistances d'accès de ces deux diodes. (1 pt)

$$V_{S1} = 0.2 \text{ V}$$

$V_{S2} = 0.1 \text{ V}$

$$R_{\rm S1} = 40~\Omega$$

$$R_{\rm S2} = 80~\Omega$$

**I.3.** A t = 0,  $E_G$  a une valeur nulle (= 0). Tracer la droite de charge sur la figure (I.2.a) et donner la valeur du courant  $I_D$  et de la tension  $V_D$ . (0.5 pt)

$$I_D = 0 V_D = 0$$

**I.4.** La variation temporelle de  $E_G$  est donnée par  $E_G = 0.5.\sin(\omega t)$  avec  $\omega = 2\pi/T$ .

**I.4.a.** Tracer sur la figure (I.2.a) les droites de charges qui correspondent aux valeurs minimale et maximale de E<sub>G</sub>. (1 pt)

**I.4.b.** A partir de la question (I.4.a.) donner les valeurs minimales et maximales de  $I_D$  et de  $V_D$  (1 pt)

$$I_{Dmin} = -3 \text{ mA}$$

$$I_{Dmax} = 3.3 \text{ mA}$$

$$V_{Dmin} = -0.35 \text{ V}$$

$V_{Dmax} = 0.33 \text{ V}$

| Brouillon |  |  |

|-----------|--|--|

|           |  |  |

|           |  |  |

|           |  |  |

|           |  |  |

|           |  |  |

|           |  |  |

|           |  |  |

|           |  |  |

|           |  |  |

|           |  |  |

|           |  |  |

|           |  |  |

|           |  |  |

|           |  |  |

|           |  |  |

|           |  |  |

|           |  |  |

|           |  |  |

|           |  |  |

|           |  |  |

|           |  |  |

|           |  |  |

|           |  |  |

|           |  |  |

**I.4.c.** A partir du schéma électrique du circuit et de l'équation de chaque diode, déterminer à nouveau les valeurs minimales et maximales de  $I_D$  et de  $V_D$  en justifiant vos résultats (2 pts)

Pour la valeur max, seul la diode  $D_1$  est passante ( $E_G > 0$ ) donc on a  $V_D = V_{S1} + R_{S1}.I_D$

La loi des mailles dans le circuit (avec thévenin équivalent) s'écrit :

$${\rm E_{G}} = {\rm R.I_{D\,max}} + {\rm V_{S1}} + {\rm R_{S1}.I_{D\,max}} \quad {\rm soit} \quad {\rm I_{D\,max}} = \frac{{\rm E_{G}} - {\rm V_{S1}}}{{\rm R} + {\rm R_{S1}}} = 3.33 {\rm mA}.$$

et

$$V_{Dmax} = V_{S1} + R_{S1}.I_{Dmax} = 0.33 \text{ V}$$

Pour la valeur min, seul la diode  $D_2$  est passante ( $E_G < 0$ ) donc on a  $V_D = -V_{S2} + R_{S2} \cdot I_D$

La loi des mailles dans le circuit (avec thévenin équivalent) s'écrit :

$$E_G = R.I_{D\,min} - V_{S2} + R_{S2}.I_{D\,min} \quad \text{soit} \quad I_{D\,min} = \frac{E_G + V_{S1}}{R + R_{S2}} = -3.07\,\text{mA}.$$

et

$$V_{\mathrm{Dmin}}$$

=  $V_{\mathrm{S2}}$  +  $R_{\mathrm{S2}}.I_{\mathrm{Dmin}}$  =  $-$  0.35  $V$

**I.4.d.** Tracer sur la figure (I.2.b) la courbe  $I_D(t)$  sur au moins une période. On indiquera les parties où la courbe est une sinusoïde pure. (2 pt)

**I.4.e.** Tracer sur la figure (I.2.c) la courbe  $V_D(t)$  sur au moins une période. On indiquera les parties où la courbe est une sinusoïde pure. (2 pt)

| Brouillon |  |  |

|-----------|--|--|

|           |  |  |

|           |  |  |

|           |  |  |

|           |  |  |

|           |  |  |

|           |  |  |

|           |  |  |

|           |  |  |

|           |  |  |

|           |  |  |

|           |  |  |

|           |  |  |

|           |  |  |

|           |  |  |

|           |  |  |

|           |  |  |

|           |  |  |

|           |  |  |

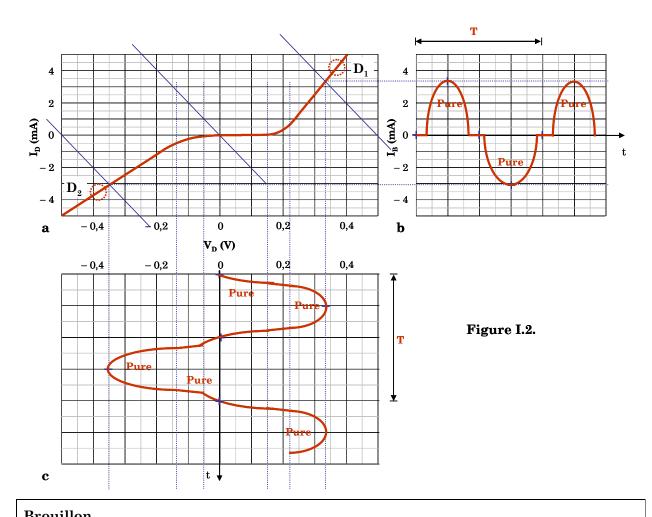

La figure (II.1) présente le schéma électrique d'une des portes logiques du processeur 1401 d'IBM sorti en 1959. Les éléments du montage sont :  $R_1 = 15 \text{ k}\Omega$ ,  $R_2 = 430 \Omega$ ,  $R_3 = 220 \Omega$ ,  $L = 56 \mu\text{H}$ .

Les paramètres du transistor NPN sont  $\beta$  = 100,  $V_{CEsat}$  = 0,2 V, le seuil de la base est de 0,6 V et la tension  $V_{BE}$  ne dépasse pas cette valeur (résistance d'accès nulle de la diode base - émetteur)

Les deux diodes  $D_1$  et  $D_2$  sont identiques avec  $V_S = 0.15 \; V$  et  $R_S = 0 \; \Omega$

Les entrées logiques A et B peuvent prendre les valeurs 6 V (1 logique) et - 6 V (0 logique).

### <u>Il n'y a aucun courant qui passe par S.</u>

On ne considèrera pas la bobine dans l'étude du circuit (équivalente à un fil).

Figure II.1.

II.1. Les entrées A et B sont à l'état 00 (i.e. les deux à sont polarisées à - 6 V)

**II.1.a.** A partir des valeurs des tensions de seuil des diodes  $D_1$ ,  $D_2$  et base-émetteur, dire en le justifiant si le transistor bipolaire est passant ou bloqué. (1 pt)

Comme A et B sont polarisées à -6 V, les deux diodes sont passantes donc la tension sur la base du transistor est de 0.15 V et le transistor est bloqué :  $I_B = 0$

II.1.b. Déterminer le courant qui passe dans la résistance R<sub>1</sub>. (1 pt)

$$I_{R1} = I_{R1} = \frac{12 - 0.15}{15000} = 0.79 \text{mA}$$

II.1.c. Donner la valeur du courant de collecteur, Ic. (0.5 pt)

$$I_C = 0$$

Le transistor est bloqué donc  $I_C = 0$

II.1.d. Déduire de la question (II.1.c.) la valeur de la tension en S. (1 pt)

$V_S = 6 V$

II.2. Les entrées A et B sont à l'état 11 (i.e. les deux à 6 V)

II.2.a. A partir des valeurs des tensions de seuil des diodes  $D_1$ ,  $D_2$  et base-émetteur, dire en le justifiant si le transistor bipolaire est passant ou bloqué. (1 pt)

Les deux diodes sont bloquées donc le courant dans  $R_1$  peut passer dans la base du transistor et le rendre passant

II.2.b. Déterminer le courant qui passe dans la résistance R<sub>1</sub>. (1 pt)

$$I_{R1} = I_{R1} = \frac{12 - 0.6}{15000} = 0.76 mA$$

II.2.c. Donner la valeur du courant de collecteur, Ic. (1 pt)

$$I_C = \beta . I_B = 76 \text{ mA}$$

| Brouillon |  |

|-----------|--|

|           |  |

|           |  |

|           |  |

|           |  |

|           |  |

|           |  |

|           |  |

|           |  |

|           |  |

|           |  |

|           |  |

|           |  |

|           |  |

|           |  |

|           |  |

|           |  |

|           |  |

|           |  |

|           |  |

|           |  |

|           |  |

|           |  |

|           |  |

|           |  |

II.2.d. Déduire de la question (II.1.c.) la valeur de la tension en S en précisant si le transistor est saturé. (1 pt)

$$V_{\rm S} =$$

$$V_S = 6 - (R_2 + R_3)I_C = -49.4V$$

On trouve  $V_S$  inférieur à -6 V, ce qui n'est pas possible donc le transistor est saturé

Si le transistor est saturé, donner la vraie valeur de Vs.

$$V_{\rm S} = -6 + V_{\rm CEsat} = -5.8~V$$

II.3. Donner la table de vérité du circuit électrique de la figure (II.1). <u>Toute tension</u> inférieure à - 5 V sera considérée comme un 0 logique (0.5 pt)

| A | В | S |

|---|---|---|

| 0 | 0 | 1 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 0 |

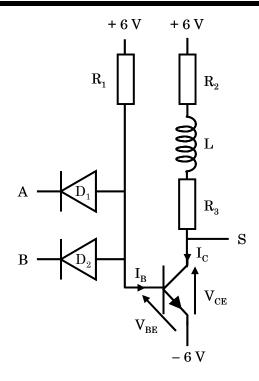

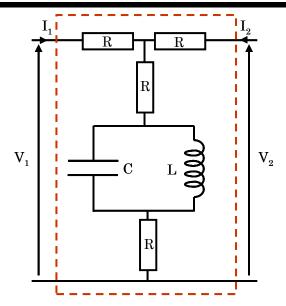

# EXERCICE III : Matrice impédance d'un quadripôle (2 pts)

III.1. (2 pt) Par la méthode de votre choix, déterminer les paramètres impédances de ce quadripôle :

(0.5 pt)

$$Z_{11} = 3R + \frac{jL\omega}{1 - LC\omega^2}$$

(0.5 pt)

$$Z_{12} = 2R + \frac{jL\omega}{1 - LC\omega^2}$$

(0.5 pt)

$$Z_{21} = 2R + \frac{jL\omega}{1 - LC\omega^2}$$

(0.5 pt)

$$Z_{22}= 3R + \frac{jL\omega}{1-LC\omega^2}$$

| ı |  |

|---|--|

| ı |  |

| ı |  |

| ı |  |

| ı |  |

| ı |  |

| ı |  |

| ı |  |

| ı |  |

| Į |  |

|   |  |